Gem5

Q&A

- How does the simulator

loadthe binary into the memory for execution?

Reference 1

A memory object:

Example system configurations in gem5/configs/:

gem5/configs/boot/: for Full-System mode. rcS files. These files will be loaded by the simulator after Linux boots and are executed by the shell.

gem5/configs/common/:

- Caches.py: example cache configuration.

- Options.py: a script to set a variety of options, such as

- number of CPUs

- system clock

- …

- CacheConfig.py: setting cache parameters for the classic memory system.

- MemConfig.py: helper functions for setting the memory system.

- FSConfig.py: Full-System simulation settings.

- see full-system chapter.

- Simulation.py: gem5 settings.

- saving/restoring checkpoints;

gem5/configs/dram/: scripts to test DRAM.

gem5/configs/example/: examples to run gem5 out-of-box

se.pyfs.py

gem5/configs/ruby/: Configuration scripts for Ruby cache coherence protocols.

gem5/configs/splash2/: Scripts to run splash2 benchmark suite.

gem5/configs/topologies/: impl of the topologies used in Ruby cache hierarchy.

se.py and fs.py

Optioins in Options.py:addCommonOptions(…)

To run:

# atomic cpu and memory (no real timing)

build/X86/gem5.opt configs/example/se.py --cmd=tests/test-progs/hello/bin/x86/linux/hello

# enable timing mode option

build/X86/gem5.opt configs/example/se.py --cmd=tests/test-progs/hello/bin/x86/linux/hello --cpu-type=TimingSimpleCPU --l1d_size=64kB --l1i_size=16kB --cachesCommon Options for se.py and fs.py

--cpu-type=--sys-clock=--cpu-clock=--mem-type=--caches--l2cache--ruby-m TICKS, --abs-max-tick=TICKS: total ticks to run simulation.-I MAXINSTS, --maxinsts=: total number of instructions to simulate.c CMD, --cmd=the binary to run in syscall emulation mode.-o OPTIONS, --options=: option passed to binary.--output=: redirect the stdout of the simulated application to a file.errout=: similar to above but stderr is redirected to a file.

- Trace Cpu

- Memory Mapping in GEM5

- Stats

- Traffic Gen

- Memory Objects in Gem5

- Extending

- Fs

- Ruby

- O3 CPU

- Arch Supports in gem5

- Gem5 KVM

Trace Creation Trace creation example: Create trace after the paddr is ready in the packet. in src/cpu/o3/probe/elastic_trace.cc: ElasticTrace::fetchReqTrace. // src/cpu/o3/probe/elastic_trace.cc // Create a protobuf message including the request fields necessary to // recreate the request in the TraceCPU. ProtoMessage::Packet inst_fetch_pkt; inst_fetch_pkt.set_tick(curTick()); inst_fetch_pkt.set_cmd(MemCmd::ReadReq); inst_fetch_pkt.set_pc(req->getPC()); inst_fetch_pkt.set_flags(req->getFlags()); inst_fetch_pkt.set_addr(req->getPaddr()); inst_fetch_pkt.set_size(req->getSize()); // Write the message to the stream. instTraceStream->write(inst_fetch_pkt); Trace reading Trace read example: read one record from trace file and create packet for replay.

Q&A Virt to Phy addr in Gem5? Binary loading (process creation) in Gem5? Reference 1 Virtual Memory Management in Gem5 Use ARM as example. TLB/Translation in ARM: src/generic/tlb.hh src/arch/arm/ table_walker.hh/cc tlb.hh/cc Physical Memory Management in Gem5 To access a memory for the packet in DRAM: src/mem/dram_ctrl.c: DRAMCtrl::accessAndRespond() -> src/mem/abstract_mem.cc: AbstractMemory::access(): To convert the Gem5 address into host machine address:

Reference 1 Gem5 Stats Package ↩

Q&A How to run traffic gen ———————– Overview (src/cpu/testers/traffic_gen/traffic_gen.hh) describes a state transition graph where each state is a specific generator behaviour. Examples include idling, generating linear address sequences, random sequences and replay of captured traces. By describing these behaviours as states, it is straight forward to create very complex behaviours, simply by arranging them in graphs. The graph transitions can also be annotated with probabilities, effectively making it a Markov Chain.

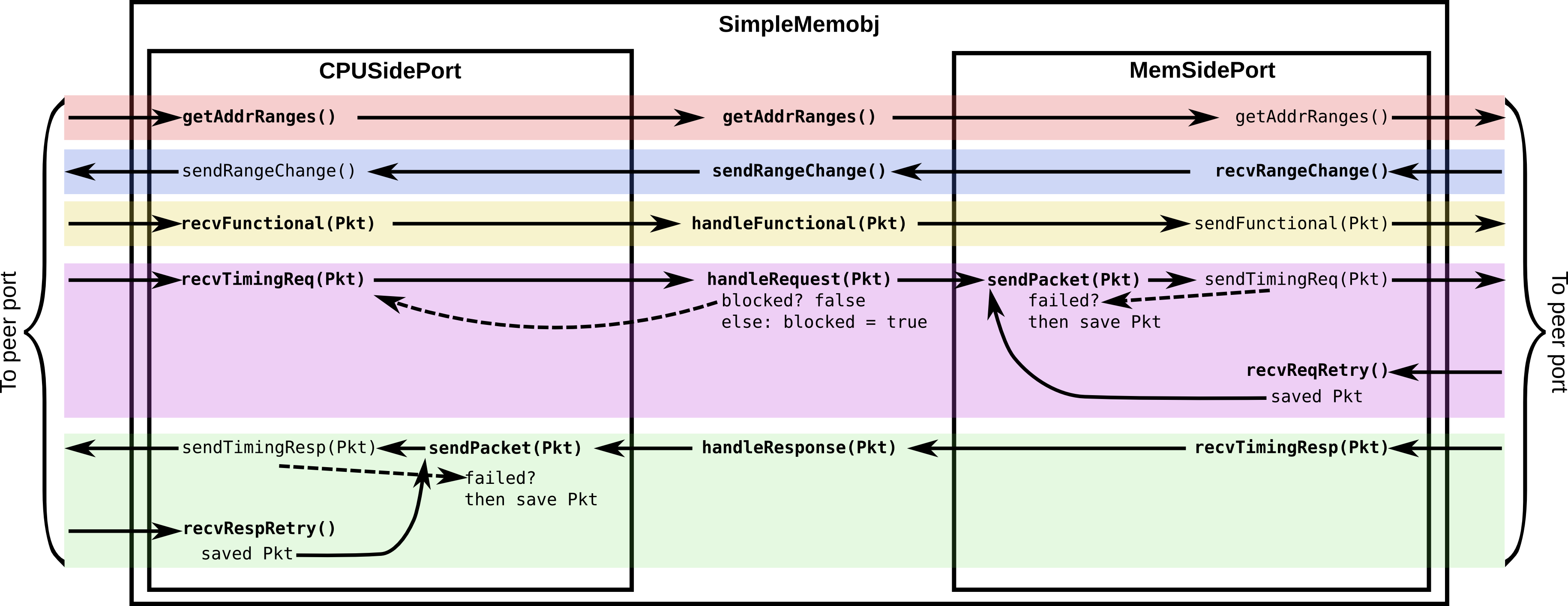

Q&A How does the memory request generated? From CPU: system.cpu = TimingSimpleCPU() see src/cpu/simple/timing.hh/cc CPU Ports: I/DcachePort -> TimingCPUPort -> MasterPort` Instruction Fetch request: TimingSimpleCPU::advanceInst >> fetch() >> thread->itb->translateTiming >> translateTiming.finish() >> sendFetch TimingSimpleCPU::schedule >> fetch() >> … >> sendFetch Instruction Fetch response: TimingSimpleCPU::IcachePort::recvTimingResp >> tickEvent.schedule >> cpu->schedule ? Instruction Exec: ? What is the binary to be executed in the simple mem object simulation?

Q&A How to replay the memory trace? How to add a last level cache/cache controller? Creating SimObject Event-driven Programming in Gem5 Debug Printing in Gem5 Reference 1 https://www.gem5.org/documentation/learning_gem5/part2/environment/ ↩

References: 2018 thesis: Simulation of RISC-V based Systems in gem5, by Robert Scheffel Full System: peripheral devices: UART, Timers More

References: Introduction to Ruby SLICC: a domain-specific language (Specification Language including Cache Coherence) for specifying coherence protocols. Files end in .sm for state machine files. Each state machine file describes states, transitions from a begin to an end state on some event, and actions to take during the transition. Coherance protocol (in SLICC) --> SLICC compiler (in Python/gem5) --> C++ files with gem5 (SimObjects, etc.) More

References: O3CPU Out of order CPU model loosely based on the Alpha 21264. Fetch Fetch instructions each cycle; Create DynInst Branch prediction Decode Decode instructions each cycle; Early resolution of PC-relative unconditional branches Rename Rename instructions using a physical register file with a free list Stall when no regs to rename to, or back-end resources have filled up Issue/Execute/Writeback Three stages combined in one stage, IEW, using execute() function Dispatching instructions to the instruction queue Telling the instruction queue to issue instruction Executing and write back instructions Commit Commit instructions each cycle; Handling any faults that the instructions may have caused; Also handles redirecting the front-end in the case of a branch misprediction.

References: From the outdated docs: Architecture Support. x86 A generic x86 CPU, with 64 bit extensions; More similar to AMD’s version of the arch than Intel’s but not strictly like either; Unmodified versions of Linux kernel can be booted in UP and SMP configurations; patches are available for speeding up boot; SSE/3dnow are implemented; no majority of x87 floating point; syscall emulation mode: both 64 and 32 bit binaries; ARM

References: x86 Full System Tutorial Tutorial: Run SPEC CPU 2017 / SPEC CPU 2006 Benchmarks in full System Mode with gem5art “gem5 features a KVM-based CPU that uses virtualisation to accelerate simulation.” In this tutorial we will build an X86 simulation, capable of running a full-system simulation, booting an Ubuntu operating system, and running a benchmark. This system will utilize gem5’s ability to switch cores, allowing booting of the operating system in KVM fast-forward mode and switching to a detailed CPU model to run the benchmark, and use a MESI Two Level Ruby cache hierarchy in a dual-core setup.

If you could revise

the fundmental principles of

computer system design

to improve security...

... what would you change?