Memory Objects in Gem5

Q&A

- How does the memory request generated?

- From CPU:

system.cpu = TimingSimpleCPU() - see

src/cpu/simple/timing.hh/cc - CPU Ports: I/DcachePort -> TimingCPUPort -> MasterPort`

- Instruction Fetch request:

- TimingSimpleCPU::advanceInst >> fetch() >> thread->itb->translateTiming >> translateTiming.finish() >> sendFetch

- TimingSimpleCPU::schedule >> fetch() >> … >> sendFetch

- Instruction Fetch response:

- TimingSimpleCPU::IcachePort::recvTimingResp >> tickEvent.schedule >> cpu->schedule ?

- Instruction Exec:

- ?

- From CPU:

- What is the binary to be executed in the simple mem object simulation?

- tests/test-progs/hello/bin/x86/linux/hello

- How does binary loaded?

Reference 1

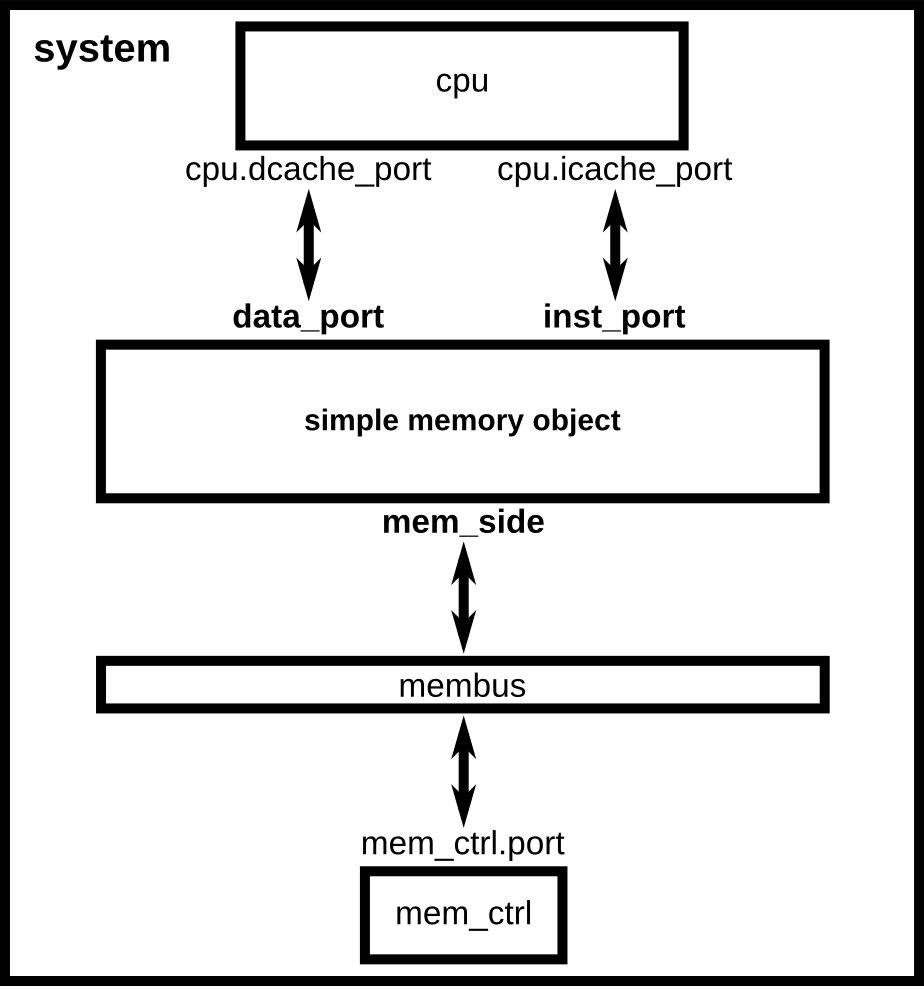

An example memory

System with a simple memory object which sits between CPU and memory bus

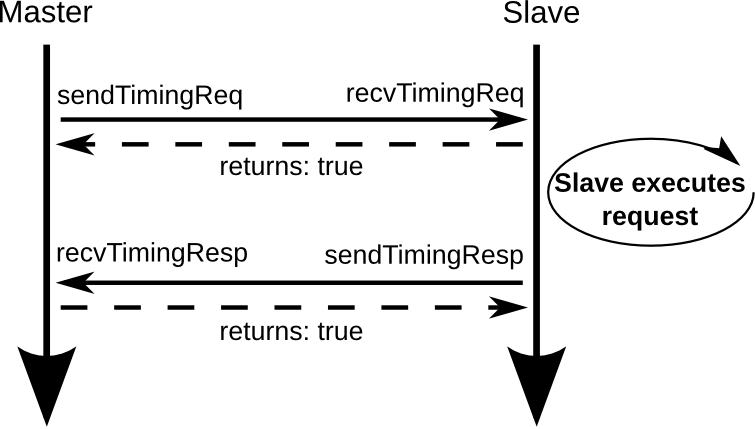

A simple master-slave interaction when both can accept the request and response:

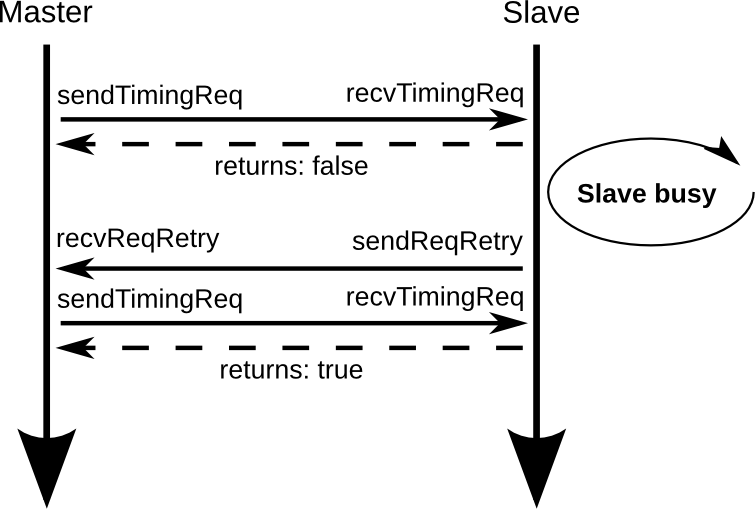

Simple master-slave interaction when slave is busy:

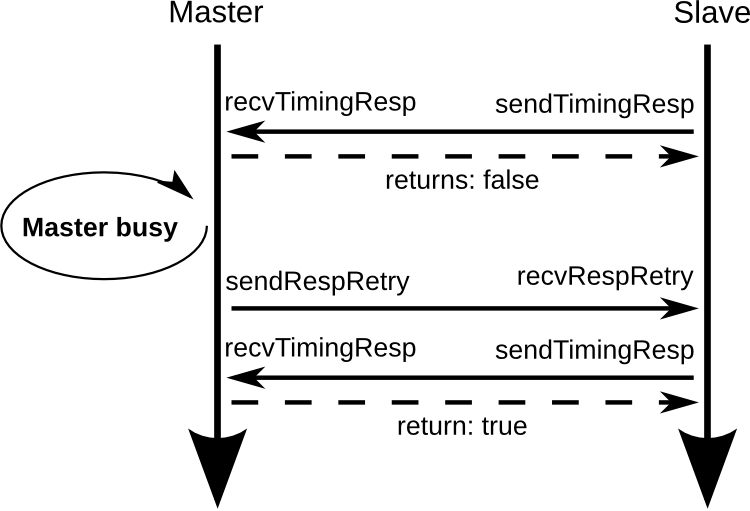

Simple master-slave interaction when master is busy:

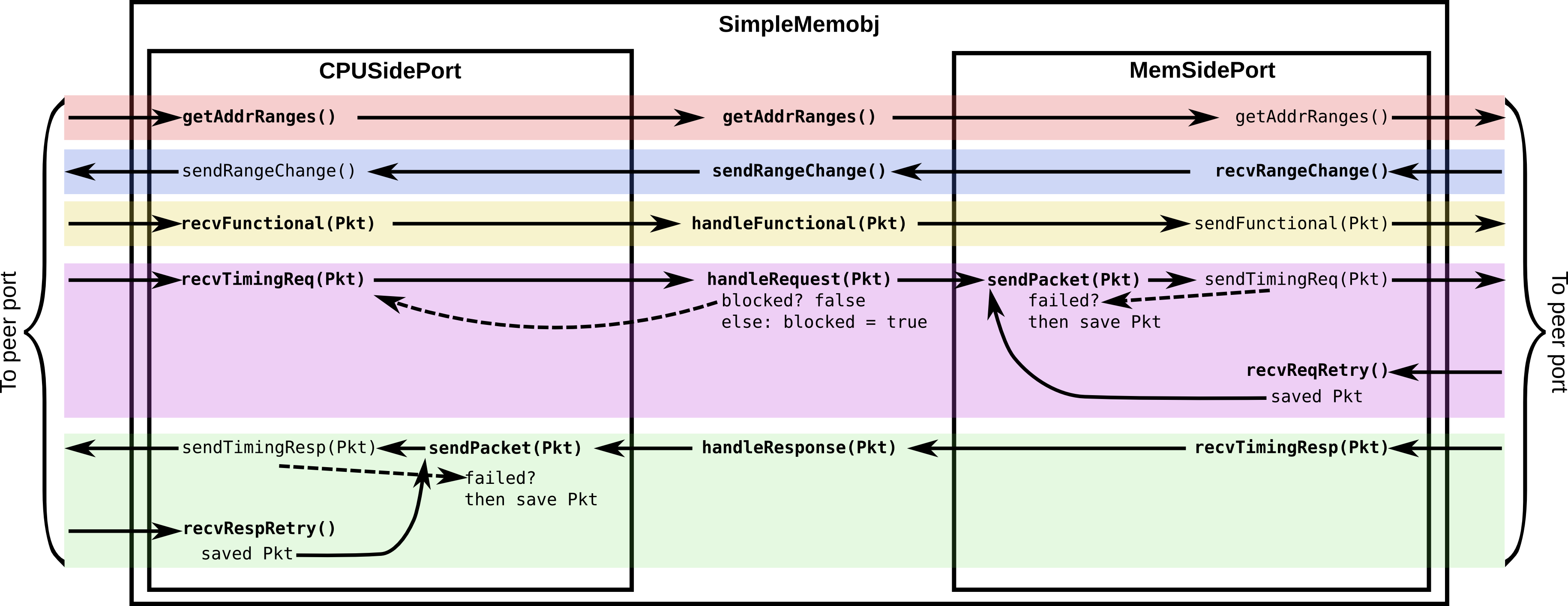

Overview of all the ports for the simple memory object:

If you could revise

the fundmental principles of

computer system design

to improve security...

... what would you change?